手法の確立と社会実装を加速しサプライチェーン全体のサイバーセキュリティ確保を目指す

発表のポイント

- ハードウェアチップに組み込まれた不正回路がサプライチェーン上での脅威になっている

- 産学官連携でハードウェアチップの設計・製造の脆弱性検知手法確立に取り組む

- 当該技術の社会実装を加速しサプライチェーン全体のサイバーセキュリティ確保に資する

2019年9月18日、学校法人早稲田大学を代表研究機関(研究責任者:理工学術院 戸川望教授、以下、早稲田大学)とし、株式会社KDDI総合研究所(以下、KDDI総合研究所)および株式会社ラック(以下、ラック)は、総務省が2019年度に実施する内閣府事業PRISM(官民研究開発投資拡大プログラム)の対象研究開発課題「設計・製造におけるチップの脆弱性検知手法の研究開発」の委託先として選定されました。

総務省 令和元年度 情報通信技術の研究開発に係る提案の公募の結果~内閣府事業PRISM(官民研究開発投資拡大プログラム)対象課題~

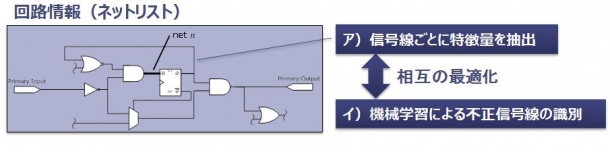

【課題Ⅰ 回路情報を用いて不正回路を検知する技術】

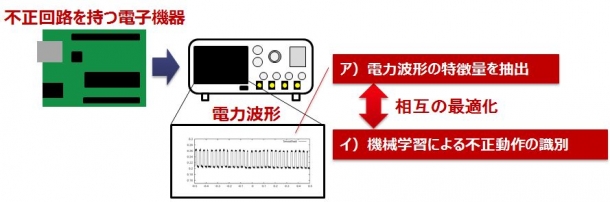

【課題Ⅱ:電子機器の外部から観測される情報を用いて不正動作を検知する技術】

(1)社会的背景、これまでの経緯

全世界の電子機器の個数は2020年には400億個を超えると予測され、新しい価値やサービスが次々と創出され人々に豊かさをもたらす一方で、複雑化するサプライチェーン全体のセキュリティ確保が重要な課題となっています。特に、電子機器のハードウェア上に組み込まれた不正なチップは製品出荷後に交換・修正することが難しく、その影響は極めて深刻になる可能性があることから、設計・製造におけるチップの脆弱性検知手法の確立は急務とされています。

(2)今回の研究で新たに実現しようとすること

回路情報のなかに不正に改変された回路が含まれるか、機械学習等のAIを活用して検知する技術の確立を目指します。

- 課題Ⅰ 回路情報を用いて不正回路を検知する技術

(ア) 不正回路について、その種類及び機能を明確化したうえで、不正回路と不正でない回路とを識別するための特徴量を抽出する技術の研究開発。

(イ)AIを活用し不正回路の特徴量と不正でない回路の特徴量を学習することにより、不正回路の有無及び不正回路の存在する位置を検知する技術の研究開発。

電力波形の特定部分の電力量や継続時間等、電子機器の外部から観測される情報を用いて、不正動作を機械学習等のAIを活用して検知する技術の確立を目指します。

- 課題Ⅱ 電子機器の外部から観測される情報を用いて不正動作を検知する技術

(ア)組み込みマイコンやFPGA等のチップに不正回路が含まれることを想定し、その動作をモデル化。当該モデルに基づき、電子機器の外部から観測される情報より、不正動作と正常動作を識別するために有意となる特徴量を抽出する技術の研究開発。

(イ)AIを活用し不正動作の特徴量と正常動作の特徴量を学習することにより、電子機器の外部から観測される情報の中から不正動作の位置を検知する技術の研究開発。

(3)この研究により期待されること

- サプライチェーン運用技術の確立

産学官連携により、ハードウェアチップの設計・製造、およびその利用における脆弱性検知手法、ならびにサプライチェーン上での運用技術を確立するとともに、当該技術の社会実装を加速する。

- 国際競争力強化

安全なハードウェアチップの設計・製造に関する特許取得、業界標準化、国際標準化、情報発信等を通じて、同分野における「国際的ハブ」の構築を図り、これを活用し国内外の半導体設計メーカーが参画する仕組みを構築。これによって我が国の国際競争力強化に寄与する。

(4)各機関の役割

課題Ⅰ-ア①:不正回路を識別するための特徴量抽出技術に関する要素技術開発

課題Ⅱ-ア :外部情報を取得する電子機器の動作のモデル化技術

課題Ⅰ-ア②:設計・製造におけるチップの脆弱性検知手法に関する動向調査

課題Ⅰ-イ :AI/機械学習に基づく不正回路検知技術に関する研究開発

課題Ⅱ-イ :AI/機械学習に基づく不正動作検知技術に関する研究開発

(5)用語解説

平成28年12月に総合科学技術・イノベーション会議と経済財政諮問会議が合同でとりまとめた「科学技術イノベーション官民投資拡大イニシアティブ」に基づき、600兆円経済の実現に向けた科学技術イノベーションの創出に向け、官民の研究開発投資と拡大などを目指して平成30年度に創設された制度です。

- ハードウェアトロイ

IoTの普及に伴って、ハードウェアの設計・製造の外注化が進んでいます。その結果、悪意ある第三者によってハードウェアトロイが挿入される危険性が指摘されています。ハードウェアトロイとはハードウェアに組み込まれた悪意のある機能のことで、ICチップの動作改変やICチップの故障、機密情報の流出を引き起こすなど多方面へリスクが広がる可能性があります。