IoT・情報通信技術研究者

戸川 望(とがわ のぞむ)/理工学術院教授

面積は小さく、処理速度は高く、消費電力は小さく

情報通信技術の進歩を支えてきた「ムーアの法則」に限界が近づいているといわれます。「モノのインターネット」(IoT:Internet of Things)が普及・浸透するには、その限界を超える技術が必要となるかもしれません。基幹理工学部の戸川望教授は、コンピュータの動作を担う集積回路を究極まで効率化すべく“限界の先”の研究に取り組んできました。(取材日:2017年9月7日)

情報通信技術の進歩を支えてきた「ムーアの法則」に限界が近づいているといわれます。「モノのインターネット」(IoT:Internet of Things)が普及・浸透するには、その限界を超える技術が必要となるかもしれません。基幹理工学部の戸川望教授は、コンピュータの動作を担う集積回路を究極まで効率化すべく“限界の先”の研究に取り組んできました。(取材日:2017年9月7日)

「ムーアの法則」の限界を乗り超える

集積回路の設計には、「面積は小さく、処理速度は高く、消費電力は小さく」といった効率化のための基本原則があります。面積が小さければ、その分、多くの集積回路を入れることができ、機器にさまざまな機能を加えることができます。また、処理速度が高まれば、コンピュータの処理能力が上がります。そして、消費電力が小さければ、電池切れにならず長時間にわたり機器を使うことができます。

コンピュータの頭脳部といえる集積回路(IC:Integrated Circuit)の技術進歩をめぐっては、「ムーアの法則」とよばれる経験則があります。みなさんも聞いたことのある言葉でしょう。これは「(集積回路の素子である)半導体の集積密度は、18〜24か月で倍増する」という法則で、米国インテル社を創設した一人、ゴードン・ムーアが提唱しました。この「ムーアの法則」を土台に、集積密度が倍になれば、面積は半分で済むようになり、それにより処理速度は高まり、また消費電力は小さくなるといわれてきました。つまり、「ムーアの法則」は「面積は小さく、処理速度は高く、消費電力は小さく」という進歩を表してきたものといえます。

ところが現在は、この「ムーアの法則」が示す進歩の速度が鈍化しているといわれています。半導体の集積密度を高めようと小型化をしても、それには限界があり、壁に突き当たりはじめているのです。昔と違って小型化が難しくなってきた現在、なおも「面積は小さく、処理速度は高く、消費電力は小さく」を進めるには、他の方法で機器の性能を高めていかなければなりません。そこで、同じ集積回路でも、できるだけ性能の高い回路を実装することで性能を高めるといったことに主眼が置かれてきているのです。これを実現するには、回路設計を上手くおこなう必要があります。

装置のメンテナンスフリー

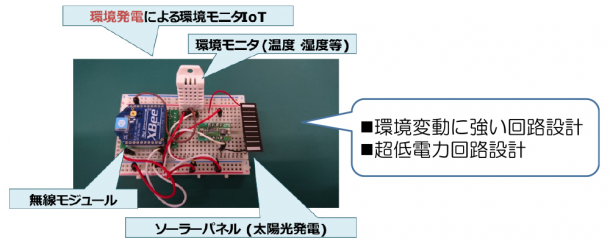

「面積は小さく、処理速度は高く、消費電力は小さく」の原則は、今も昔も重要ですが、とりわけモノのインターネット(IoT:Internet of Things)の応用がどんどん広がっていくなかで、今後、一層、重要性を高めていくものと考えられています。というのも、この先、森林や海上、さらに宇宙など、安定した電力を得られないような場所でもIoTデバイスは広く使用されることが見込まれ、それらの環境下では電力を外部から供給するのでなく、太陽光や振動などの環境由来のエネルギーで自給自足することが必要となるからです。

たとえば、太陽光や風力、また振動といった環境エネルギー由来の電気だけで、状況に応じて最適に動作するコンピューティングシステムは、将来のIoT社会を支えるものになると考え、新たなシステムを構築すべく研究をしています。

図:振動や太陽光などを由来とする環境発電により作動する回路の設計(出典:戸川研究室)

また、IoTデバイスは人のアクセスしづらい場所でも利用されるため、部品交換を簡単にはできない場合もあります。そこで、装置そのものがメンテナンス不要で長時間、安定して動くことも重要となるのです。これらを実現するため、私たちの研究室では、その主要部品である集積回路(IC:Integrated Circuit)に着目しています。

FPGAの性能向上をめざして

「面積は小さく、処理速度は高く、消費電力は小さく」をさらに実現していくため、FPGAという集積回路を対象とした研究を続けてきました。FPGAは、“Field-Programmable Gate Array”の頭文字をとったもので、「電気的に書き換え可能な回路」のことを指し、プログラミングによって回路の内部を書き換えることで、その回路をまったく別の動作をする回路に生まれ変わらせることができます。 FPGAを使うと、もし、回路にバグがあることが見つかったとしても、後からプログラムを修正して書き換えることができるのです。FPGAはとても使いやすい集積回路です。

私自身が大学学部生時代から博士課程にかけて取り組んできた研究のテーマが、このFPGAに対して設計を工夫することで「面積は小さく、処理速度は高く、消費電力は小さく」を実現することでした。学部生から修士課程に進むころの1990年代序盤にFPGAは世に出まわりはじめました。どのようにすればFPGAの速度が速くなるか、またどうすれば使用電力を小さくできるかは、まだ未解明の状況でした。そこで、FPGAでどのように「密度は高く、処理速度は高く、消費電力は小さく」を実現するのかを研究し、それを「FPGAを対象とした設計自動化手法に関する研究」というタイトルの論文にまとめたのです。

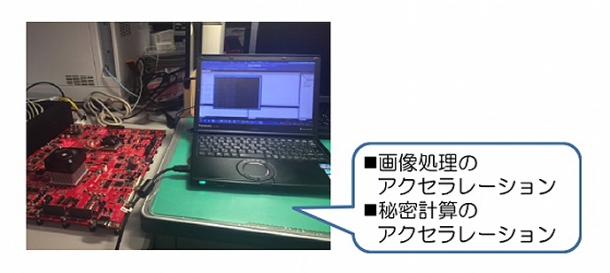

図:画像処理や秘密計算をおこなうFPGAの高速化(アクセラレーション)に関わる技術の研究を現在も行っている(出典:戸川研究室)

写真:研究室の学生たちが取り組んだ回路設計。情報処理学会のアルゴリズムデザインコンテストに研究室として参加、最優秀賞に輝いた

工学の研究は、研究者の好奇心が推進力になることのほかに、社会に役立つものを作る必要性が推進力になる側面もあります。当時は、FPGAをいかに活用するかという社会の要請がありました。世に出始めたばかりの素子だったので、資料やノウハウが乏しく、研究するのは大変でしたが、やりがいのある研究でした。集積回路のひとつとしてFPGAは多くの電子機器に汎用的に使われるようになりました。現在もFPGAを用いた画像処理や秘密計算の処理速度の向上を、研究テーマのひとつにしています。

次回は、研究・教育に対する思いやモットー、また早稲田大学の学生像についてお話しいただきます。

☞1回目配信はこちら

☞2回目配信はこちら

☞4回目配信はこちら

プロフィール

戸川 望(とがわ のぞむ)

戸川 望(とがわ のぞむ)

1997年早稲田大学大学院理工学研究科電気工学専攻博士後期課程修了(博士(工学))。早稲田大学理工学部電子・情報通信学科助手、北九州市立大学国際環境工学部助教授、早稲田大学基幹理工学部情報理工学科准教授などを経て、2009年より早稲田大学理工学術院教授(基幹理工学部)。専門は、集積回路設計とその応用技術、セキュリティ技術。電気通信普及財団テレコムシステム技術賞(2011年)ほか受賞多数。

詳しくは戸川研究室

業績情報

論文

- Hardware Trojans classification for gate-level netlists based on machine learning (2016 IEEE 22nd International Symposium on On-Line Testing and Robust System Design, 2016, p.203-206)

- A score-based classification method for identifying Hardware-Trojans at gate-level netlists (Design, Automation & Test in Europe Conference & Exhibition, 2015, p465-470)

- A Stayed Location Estimation Method for Sparse GPS Positioning Information (2017 IEEE 6th Global Conference on Consumer Electronics, 2017)

- An Accurate Indoor Positioning Algorithm using Particle Filter based on the Proximity of Bluetooth Beacons (2017 IEEE 6th Global Conference on Consumer Electronics, 2017)

受賞

1994年度 電気通信普及財団第10回テレコムシステム技術学生賞

1995年度 IEEE Asia and South Pacific Design Automation Conference

1995年度 ASP-DAC’95 Best Paper Award

1995年度 早稲田大学平成7年度大川功記念賞

1995年度 早稲田大学平成7年度小野梓記念学術賞

1996年度 電子情報通信学会第8回回路とシステム軽井沢ワークショップ研究奨励賞

1996年度 安藤研究所第9回安藤博記念学術奨励賞

1997年度 丹羽記念会平成9年度(第21回)丹羽記念賞

2001年度 武田計測先端知財団、武田研究奨励賞優秀賞

2009年度 丸文研究交流財団、丸文研究奨励賞

2009年度 船井情報科学振興財団,船井学術賞

2010年度 電気通信普及財団、テレコムシステム技術賞