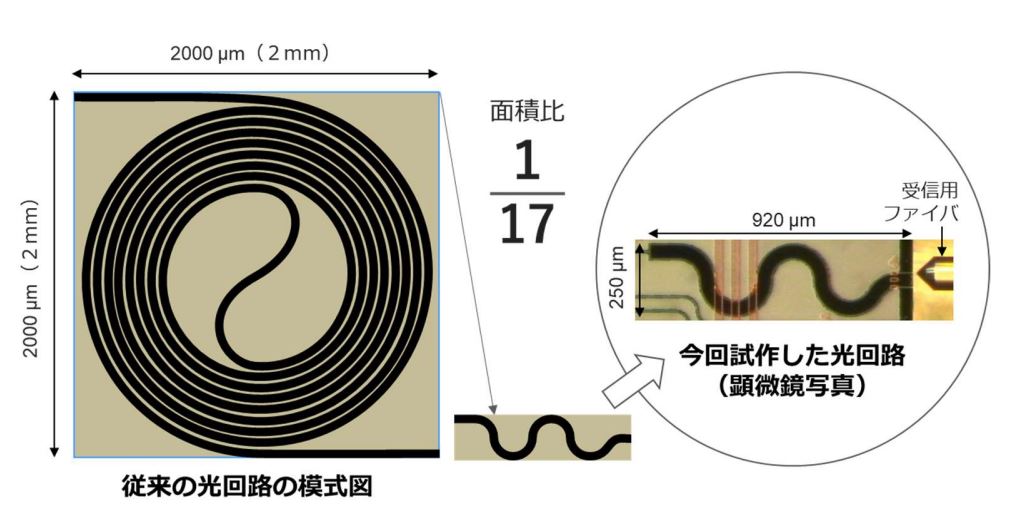

低消費電力AIを実現するシリコン光回路を従来比17分の1のサイズにコンパクト化、AIの基本動作の実証に成功

株式会社KDDI総合研究所(本社:埼玉県ふじみ野市、代表取締役所長:中村 元)と学校法人早稲田大学(本部:東京都新宿区、理事長:田中 愛治、責任者:宇髙 勝之 教授)は、AIの低消費電力化と高速化の実現を目指し、従来比で約17分の1の面積の光AIアクセラレーター用シリコン光回路を試作し、時系列データの予測を行うことに成功しました。AIの活用は拡大の一途をたどっており、莫大な数のコンピューターが必要とされています。KDDI総合研究所と早稲田大学はさらなる研究開発を進め、低消費電力、高速な光AIアクセラレーターの実用化に向けた基盤技術の確立を目指していきます。

【背景】

自然な文章を生成するAIを使ったチャットボットが公開され、世界中の注目を集めています。このような最先端を走るAIを動作させるためには莫大な数のコンピューターが必要であり、消費電力の削減や処理の高速化が課題となっています。一般に用いられるAIは電子回路上で動作していますが、一部の演算を光回路に置き換える光AIアクセラレーターは、消費電力の削減に有効で、かつ学習や推論の高速化が可能なことから、研究開発が盛んになっています。

中でもシリコン上に形成した光回路は、電子回路や他の光素子との集積化が容易な上、小型化できると期待されています。一方で光アクセラレーターを実用化するには、大規模に集積しやすくする必要があり、より一層の小型化が求められています。

【今回の成果】

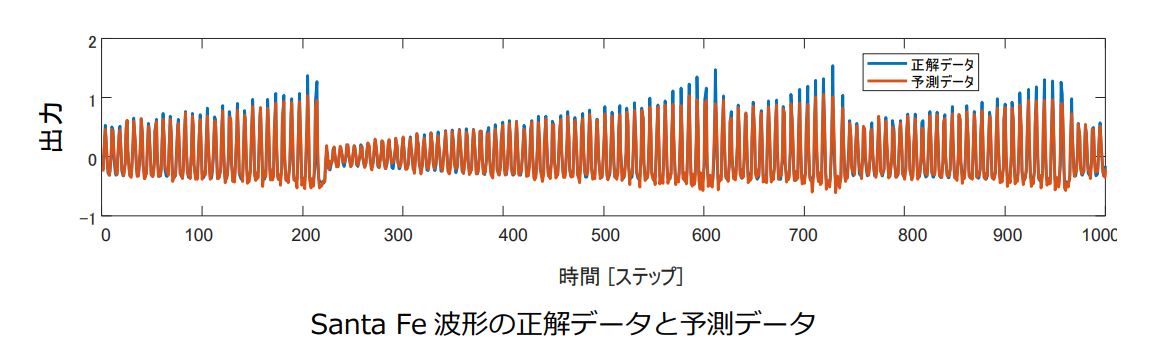

KDDI総合研究所と早稲田大学は、従来比で約17分の1の面積の光AIアクセラレーター用シリコン光回路を試作し、時系列データの予測を行うことに成功しました。シリコン上に光回路(面積:0.25mm×0.92mm)を試作し、性能比較のため標準的に用いられているタスクであるSanta Fe波形(注1)の予測をさせたところ、正解データと予測データの誤差が非常に小さく、その構造の有効性を示すことができました。

【回路面積縮小の工夫】

これまで研究されてきたシリコン上に形成した光回路では、AIのモデルの一つであるリザバーコンピューティング(注2)を動作させるために、現在の情報と過去の情報を混ぜ合わせる必要があり、以下のいずれかの構造を採用していました。

- 信号をネットワーク状に形成された光回路で何度も混ぜ合わせる構造

現在の情報と過去の情報が効果的に混ざるようなタイミングとするためにネットワークの節間の距離を確保する必要があり、素子面積が広くなる(16mm2)。ニューロン数(神経細胞数)を増やすとさらなる面積が必要。

- 長い渦巻き状マルチモード光導波路構造

進む速度が異なる光波が多数存在できるマルチモード光導波路の性質を利用して現在の情報と過去の情報とを混ぜ合わせるために長い(4cm程度)光導波路が必要とされる。渦巻き状に収容しても2mm ×2mm 程度の面積が必要。

今回の試作では、構造2に比べて導波路幅を2倍広くし、さらには蛇行状の導波路構造を採用して長さを調整することにより、短い導波路長でゆっくりと進む光波(高次モード)を多数発生させ、さらには信号の高速化することで現在の情報と過去の情報が十分に混ざり合うように設計しました。

なお、今回の成果は米国サンノゼで開催される光エレクトロニクス関連の総合的な国際学術会議CLEO2023(The Conference on Lasers and Electro-Optics)において採択され、2023年5月8日(現地時間)に発表します。

【今後の展望】

光AIアクセラレーターがさまざまなシーンで利用されるように、光回路の構造探索や規模拡大を進め、GPUベースのAIアクセラレーターに比べて10分の1の低消費電力、かつ高速な光AIチップの基盤技術の確立を目指します。

■ KDDI総合研究所の取り組み

KDDI総合研究所は、2030年を見据えた次世代社会構想「KDDI Accelerate 5.0」を策定し、その具体化に向け、イノベーションを生むためのエコシステムの醸成に必要と考えられる「将来像」と「テクノロジー」の両面についてBeyond 5G/6Gホワイトペーパーにまとめました。新たなライフスタイルの実現を目指し、7つのテクノロジーと、それらが密接に連携するオーケストレーション技術の研究開発を推進します。今回の成果は7つのテクノロジーの中の「ネットワーク」に該当します。

■ 早稲田大学の取り組み

早稲田大学では、現在全学でカーボンニュートラル社会を目指した研究教育体制の構築に取り組んでいます。その中で、一層進展する高度情報化社会のための低消費電力大容量ネットワーク技術と並んでAIなどの高度情報処理技術の高速化・低消費電力化が不可欠と考えており、シリコンフォトニクス集積回路(SiPIC: Si Photonic Integrated Circuits)を用いた光信号処理デバイス技術の検討と実証を目指しています。

(注1)1992年に米国のSanta Feで開催された時系列予測コンテストにおいて使用された時系列データで、不安定なレーザーから出力されたパワー変動を記録したもので、予測性能を評価するときに標準的に用いられるデータの一つ。

(注2)時系列データの予測に主に適用される機械学習の手法の一つで、入力層、リザバー層(ランダムにニューロンが接続された層)、出力層からなる構造を有する。学習により出力層の結合の重みだけを変える単純さが特徴で、それにより高速な学習が可能となる。