技術開発のロードマップにも影響する理論的限界を解明―理工・渡邉研

早稲田大学理工学術院(新宿区大久保3-4-1)の渡邉孝信教授、神岡武文次席研究員らは、電子がバラバラの粒子であることから生じる本質的な電流雑音により、半導体LSIの高性能化の限界が決まることを、シミュレーションを用いた検討によって明らかにしました。数10GHzから100GHzの動作周波数領域で、LSIの素子を流れる電子の数が大きくばらつき、正常に動作しなくなると予測されます。電子数の変動による雑音は本質的に避けられないため、これがLSIの動作周波数の限界を決定すると考えられます。これらの成果は、半導体デバイスの高速化や省電力化の理論的限界を明らかにしたという点で、今後の半導体集積回路技術開発のロードマップに影響を与えるものとなります。なお、本研究はJSTの戦略的創造研究推進事業 チーム型研究(CREST)の一環として行われました。

今回の研究成果については、米・サンフランシスコで12月10~12日(現地時間)に開催される「国際電子デバイス会議(IEEE International Electron Device Meeting; IEDM)」にて発表します。

研究概要 : 半導体LSIの性能限界 流れる電子の数で決まることを予測

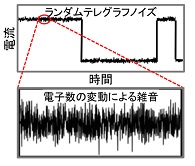

図1 デバイスの主要な雑音であるランダムテレグラフノイズ(上)と、電子数の変動による雑音(下)。

理工学術院の渡邉孝信教授、神岡武文次席研究員らは、電子がバラバラの粒子であることから生じる本質的な電流雑音により、半導体LSIの高性能化の限界が決まることを、シミュレーションを用いた検討によって明らかにしました。数10GHzから100GHzの動作周波数領域で、LSIの素子を流れる電子の数が大きくばらつき、正常に動作しなくなると予測されます。

半導体LSIの性能は、LSIを構成する素子の微細化と高集積化により向上してきました。しかし近い将来、1つの素子の寸法が10 nm程度(1ナノメートル、1 nm = 10-9 m)まで小さくなると、電流雑音が増加し、高速動作させた場合に動作不良が起こりやすくなると予想されています。このため、電流雑音を抑制する技術が世界で盛んに研究されています。

電流雑音の原因のうち、現在おもに問題となっているのは、ランダム・テレグラフ・ノイズと呼ばれる雑音です。これは、素子を覆う絶縁膜中の欠陥部位に、電子が捕獲、あるいは放出されることによって生じると考えられています(図1上段)。一方、素子の中を流れる電子の個数が変動することで生じる本質的な電流雑音もありますが、これまであまり注目されてきませんでした(図1下段)。

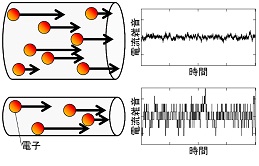

図2 電子数の変動による雑音。電子数が少なくなると、雑音の相対的な大きさが信号と比べて無視できなくなる。

渡邉教授と神岡研究員らは、ナノメートルかつピコ秒(1ピコ秒、1 ps = 10-15秒)程度の、空間的にも時間的にも限定されたモデルを用いた電気伝導のシミュレーションを行い(図2)、ランダム・テレグラフ・ノイズと、電子数の変動による雑音の影響を比較しました。その結果、周波数が高くなると、電子数の変動による雑音がランダム・テレグラフ・ノイズを必ず上回ることを明らかにしました。

このまま微細化と高速化を推し進めていくと、数10GHzから100GHzの動作周波数で逆転すると予測されます。ランダム・テレグラフ・ノイズは、欠陥を少なくするなど、半導体LSIの製造方法を改善すれば抑制できる可能性がありますが、電子数の変動による雑音は本質的に避けられないため、これがLSIの動作周波数の限界を決定すると考えられます。

これらの成果は、半導体デバイスの高速化や省電力化の理論的限界を明らかにしたという点で、今後の半導体集積回路技術開発のロードマップに影響を与えるものとなります。

論文について

IEEE International Electron Device Meeting (IEDM)で発表決定

神岡武文2,5、今井裕也1,5、鎌倉良成3,5、大毛利健治4,5、白石賢二4,5、丹羽正昭4,5、山田啓作4,5、渡邉孝信1,2,5

(1 早稲田大学理工学術院、2 早稲田大学ナノ理工学研究機構、3大阪大学大学院工学科、4筑波大学大学院数理物質科学研究科、5 JST-CREST)

リンク

以上