超高精細な動画像の普及に期待―IPS後藤研究室

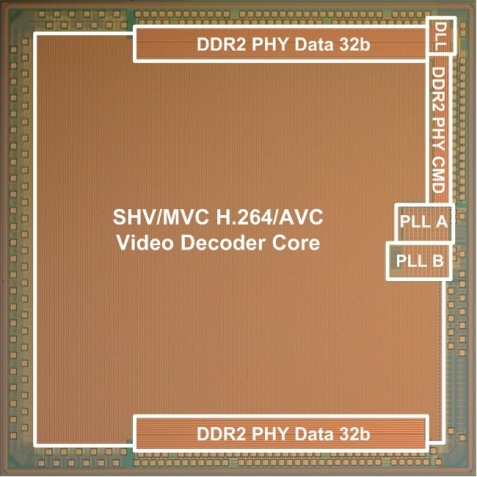

開発したチップ

早稲田大学大学院情報生産システム研究科(北九州市若松区)の後藤敏研究室は、ハイビジョンの16倍となる超高精細の解像度を実現したスーパーハイビジョン向けのビデオ復号LSIの開発に、世界で初めて成功しました。家庭や携帯端末等で使用するためには小型化と低消費電力化が要求されるため、その実現のためには本研究で開発した復号機能を1チップで実現するビデオデコーダが強く要請されていました。この研究成果については2012年2月21日、米国サンフランシスコ市で開催されたISSCC (International Solid-State Circuits Conference, 2012) にて発表いたしました。

研究概要:スーパーハイビジョン用ビデオ復号LSI

ビデオデータはそのままのデータはサイズが極めて大きいために、1/10~1/20程度の圧縮処理を行い(符号化)、データの転送後、伸張処理(復号化)でデータを復元することが行われます。ハイビジョン用ビデオは家庭用ビデオレコーダにおいて広く使われてきており、圧縮方式としてMPEG2と呼ばれる世界標準規格が使われてきました。最近、圧縮度を約2倍に向上させたH.264規格が使用され始め、画素数も現在の衛星放送等で使われているフルハイビジョン(1920×1080) に代わって、 4096×2160というより高精細なビデオカメラやレコーダが注目され、製品化も行われつつあります。

今回開発したスーパーハイビジョン用ビデオ復号LSIは、更に高精細な(7680×4320)というハイビジョンの16倍の画素数の動画が扱えるものです。家庭や携帯端末等での使用のためには小型化と低消費電力化が要求され、復号機能を1チップで実現するビデオデコーダの開発が強く要請されていました。

開発したビデオ復号LSIの特徴は以下の通りです。

- H.264/AVC ハイプロファイル標準仕様に基づくデコーダで、7680×4320画素の動画を60枚/秒処理できます。また、3次元/マルチビュービデオ対応として、ハイビジョン(760p)では32画面、フルハイビジョン(1080P)では16画面の復号60枚/秒の処理が可能です。

- 画像フレームを並列する方式を導入し、復号処理を2並列、エントロピー処理を4並列化することで2Gピクセル/秒の高速化を図り、上記の性能を達成することができました。

- 2レベルキャッシング、参照フレーム同期方式等の新技術を開発することで、外部DRAMとデコーダエンジン間の転送量を従来と比べて24%削減しました。

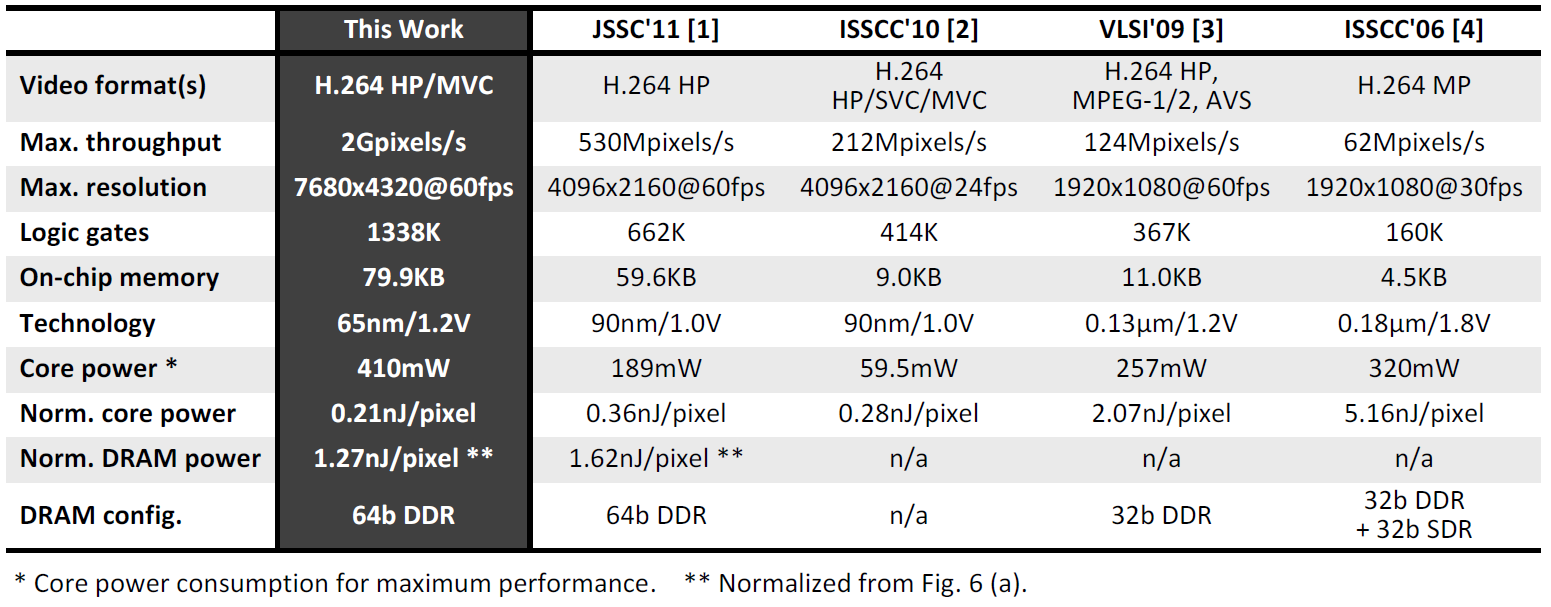

- 復号チップの回路規模は1.3Mゲート(ロジック)と80Kバイト(メモリ)で電力消費も7680×4320@60fpsで410mWを達成し(SMIC 65nmルール)、従来の復号チップに比べて、約42%の消費電力削減を図りました(設計ルールが異なるためスケーリングを行った結果)。

NHKは2020年にスーパーハイビジョンの試験放送を予定しており、今回、極めて低消費電電力で回路規模の小さな1チップのLSIを開発できたことで、スーパーハイビジョンの実用化が近づいたと考えられます。本研究開発は文部科学省が福岡県へ委託した地域イノベーションプロジェクトの中で生まれたであり、今後、成果を企業へ移転し実用化に向けて努力する予定です。

発表論文

Dajiang Zhou1, Jinjia Zhou1, Jiayi Zhu2, Peilin Liu2, and Satoshi Goto, “A 2Gpixel/s H.264/AVC HP/MVC Video Decoder Chip for Super Hi-Vision and 3DTV/FTV Applications,” International Solid-State Circuits Conference (ISSCC 2012)

1 Graduate School of Information, Production and Systems, Waseda University, 2-7 Hibikino, 808-0135, Japan

2 Department of Electronic Engineering, Shanghai Jiao Tong University, China

[1]D.Zhou, et al, IEEE JSSC, Vo.46, No.4, pp.777-788, April 2011.

[2]T-D, Chang, et al, ISSCC, pp.330-331, 2010.

[3]D. Zhou, et al, Symp. VLSI circuits, pp.262-263, 2009.

[4]C.-C. Lin, et al.,IEEE JSSC, vol. 42, no. 1, pp. 170–182, Jan. 2007.

従来の成果との性能比較

リンク