理工学術院・渡邉孝信教授、大学院先進理工学研究科の鈴木晃人氏(修士課程2年)らの研究グループは、スマートフォン等の電子機器の処理能力を左右する、半導体LSIの基本素子・MOSトランジスタの集積化限界を決める要因を明らかにすることに成功し、米・サンフランシスコで開催された半導体関連研究分野における世界最先端の国際会議「IEEE International Electron Device Meeting(IEDM)」(2014年12月13~17日)で成果発表しました。鈴木氏は修士課程2年生の大学院生であり、卒業研究の頃から独自に開発した手法によってIEDMで認められる成果を挙げたことは快挙といえます。

今回の研究では、ナノワイヤ型MOSトランジスタ(応答速度が速く、低消費電力で動作させることが可能な次世代型MOSトランジスタ)に含まれる全ての電子や不純物を粒子として扱うことで、原子レベルの配置の違いが引き起こすデバイス特性の統計的解析を実現しました。また、トランジスタ内の電子の軌跡を全て計算することで、動的な電流揺らぎの解析を行うことも可能にしました。さらに、MOSトランジスタ間の各特性ばらつきの要因が集積化に与える影響を明らかにし、今後の半導体回路技術開発のロードマップに影響を与えることが期待されます。また、本シミュレータの開発においては、動画編集やゲーム等で使われる描画処理に特化した専用ハードウェア・グラフィックスチップ(Graphic Processing Unit)が、単純な演算の繰り返しに適していることに注目し、MOSトランジスタに含まれる電子や不純物等の粒子の軌跡計算に用いました。MOSトランジスタに含まれる粒子の計算を全て同時に行うことで、計算時間を大幅に短縮することに成功し、数千粒子を含む大規模な計算モデルでは、10倍以上高速に計算することが可能になりました。本シミュレータは、コストパフォーマンスが極めて高く、モデルの形状や計算規模に対して高い自由度を与え、トランジスタの研究を促進させることが見込まれます。

ゲーム等で使われるグラフィックスチップ(GPU)を用いて半導体LSIの基本素子・MOSトランジスタの性能限界予測に成功

(1) MOSトランジスタの性能予測は必要不可欠

スマートフォンなどの電子機器の処理速度は、半導体LSIの性能によって決まる。半導体LSIの進歩は、LSIを構成する基本素子であるMOSトランジスタの微細化によって牽引されてきた。トランジスタを微細化することで、同一面積内により多くのトランジスタを集積することができるだけでなく、動作速度の向上や消費電力の削減が可能になるからである。しかし、微細化が進むにつれリーク電流などの問題が生じ、MOSトランジスタの構造や加工技術がどんどん複雑になり、開発コストの増大が顕著になっている。その結果、シミュレーションによるMOSトランジスタの性能予測が必要不可欠となっている。

MOSトランジスタの微細化が極限まで推し進められた結果、電子や不純物が粒子であることによる影響が無視できなくなっている。電子や不純物を連続体として扱うことができないため、MOSトランジスタを構成する全ての粒子間に働く力を計算する必要がある。さらに、LSIとして集積化した際に問題となってくるMOSトランジスタ間の特性ばらつきの影響も考慮する必要があるため、MOSトランジスタの性能を正確に予測するためには、1つのデバイスモデルにつき数十回に渡る統計的解析を行う必要がある。従って、粒子ベースの半導体シミュレータの大幅な高速化・大規模化が必要不可欠である。

(2) 集積化限界を決める大きな要因

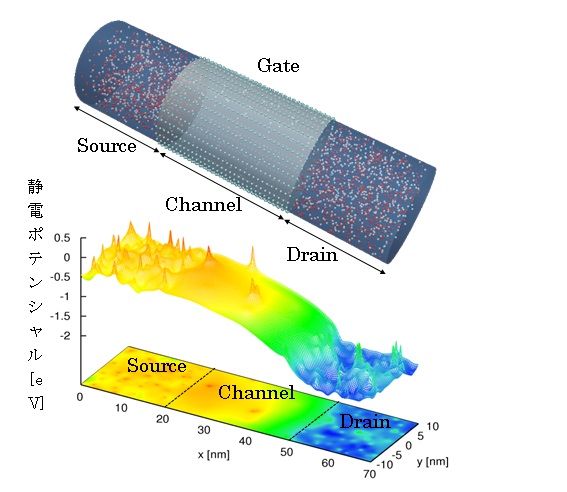

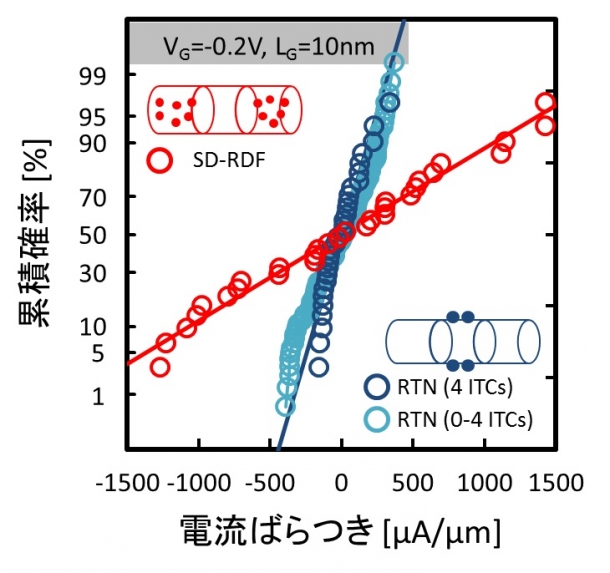

近年、リーク電流に強い構造としてナノワイヤ型のMOSトランジスタが注目されている。今回の研究では、ナノワイヤ型トランジスタに含まれる電荷を粒子として扱う粒子ベースの半導体シミュレータの開発を行った。トランジスタに含まれる全ての電荷を粒子として扱うことで、原子レベルの配置の違いが引き起こすデバイス特性の統計的解析を実現した。また、トランジスタ内の電子の軌跡を全て計算することで、動的な電流揺らぎの解析を行うことも可能にした。LSIの高集積化を阻む特性ばらつきとして注目されているのが、ソース・ドレイン内の不純物の位置の違いによる統計的ばらつきと、動的な揺らぎであるランダム・テレグラフ・ノイズである。ランダム・テレグラフ・ノイズとは、トランジスタを覆う絶縁膜中に電子が捕獲あるいは放出されることによって生じるノイズである。本研究では、静的なばらつきであるソース・ドレイン内の不純物の位置の違いによる統計的ばらつきの影響と動的な揺らぎであるランダム・テレグラフ・ノイズの影響を比較した。結果として、ソース・ドレイン内の不純物の位置の違いによる統計的ばらつきの影響は、ランダム・テレグラフ・ノイズによる電流揺らぎに比べて圧倒的に大きく、集積化限界を決める大きな要因になることが明らかになった。

(3) Graphic Processing Unitを用いた大規模並列計算

MOSトランジスタ全体の粒子ベース・シミュレーションを可能にしたのが、描画処理に特化した専用ハードウェアであるGPU(Graphic Processing Unit)を用いた大規模並列計算である。通常、GPUは動画編集やゲームに使われることが多いが、本研究ではGPUを科学計算に用いた。1つのGPUには数百から数千個の演算ユニットが搭載されている。画像や動画の描画処理の多くが単純な演算の繰り返しであることから、同一処理の並列計算に適している。本研究では、GPUの1つの演算ユニットに対して1粒子の計算を割り当て、MOSトランジスタに含まれる粒子の計算を全て同時に行うことで、計算時間を大幅に短縮した。数千粒子を含む大規模な計算モデルでは、GPUを用いた並列計算により、10倍以上高速に計算することを可能にした。また、これらプログラムコードの開発は修士の学生一人を中心に行われたものである。

今回開発した半導体シミュレータは電子や不純物を粒子として扱うものである。この手法は、他のシミュレータで多く用いられているモデルをメッシュで区切る方法と比較し、電子や不純物が離散的であることによる影響を直接扱えるだけでなく、メッシュの区切り方に寄らず計算モデルの自由度が高い。これにより、円筒などの曲線的なモデルといったより複雑なモデリングが可能になり、新構造トランジスタの研究への応用が期待されている。

(4) MOSトランジスタの統計的解析が可能に

今回の研究により、GPUによる大規模並列計算によって半導体シミュレータの高速化を実現したことで、全てを粒子として扱うリアリスティックなMOSトランジスタの統計的解析が可能になった。この半導体シミュレータを用いることにより、不純物の位置の違いによる統計的ばらつきと、ランダム・テレグラフ・ノイズに起因する動的揺らぎを直接比較することが可能になった。ソース・ドレイン内の不純物の位置の違いによる統計的ばらつきの影響は他の要因と比べて圧倒的に大きく、集積化限界を決める大きな要因になることが明らかになった。

さらに、ソース・ドレインの不純物の位置の違いの影響を詳しく解析した結果、ソースとチャネルの界面付近の不純物の位置の違いがMOSトランジスタの特性の違いに大きく影響を与えるということを明らかにした。さらに、ソースとチャネル界面付近の不純物濃度を揃えることで、MOSトランジスタの特性ばらつきを抑えるのに効果的であることを明らかにした。

(5) GPUを使った並列計算は科学計算の分野においても必須に

GPU並列計算を用いた粒子ベースの半導体シミュレータの開発は、モデルの形状や計算規模に対して高い自由度を与え、新構造・新原理トランジスタの研究を促進させると期待している。10万円程度で入手可能なGPUであっても、一昔前のスーパーコンピュータと同程度の計算性能をもっていることから、コストパフォーマンスが極めて高い。スーパーコンピュータのような演算性能が、少ない初期コストで手に入ることから、近い将来、GPUを使った並列計算が科学計算の分野においても必須になると思われる。

本研究は、各特性ばらつきの要因が集積化に与える影響を明らかにしたという点で、今後の半導体回路技術開発のロードマップに影響を与えると思われる。また、様々な特性ばらつきの影響の大きさを比較し、最も影響を与える要因を特定することで、特性ばらつきを抑制できるデバイス構造の探索が容易となる。本研究により、不純物を使わない新しい設計方針を各半導体メーカーに与え、次世代プロセスへの投資を効率的に行うことにつながると期待している。

(6) 回路全体の包括的な特性ばらつきの解析へ

現在までに開発した技術は単一MOSトランジスタのシミュレーションであった。デバイス間をつなぐ配線によるばらつきや、金属と半導体の界面によるばらつきなども、現在の粒子ベースの半導体シミュレータに取り入れ、より現実を反映したデバイスのモデル化に努めたい。そして、MOSトランジスタを組み合わせた電子回路である、NAND型フラッシュメモリやCMOSインバータ、DRAMやSRAMの動作シミュレーションに取り組み、回路全体の包括的な特性ばらつきの解析を行っていきたい。