# Simultaneous Fabrication of a Through-Glass Interconnect Via and Bumps Using Dry Filling Process of Submicron Gold Particles

Kazuya Nomura<sup>1,\*</sup>, Akiko Okada<sup>1</sup>, Shuichi Shoji<sup>1</sup>, Toshinori Ogashiwa<sup>2</sup> and Jun Mizuno<sup>3</sup>

<sup>1</sup>Waseda University, 3-4-1 Okubo, Shinjuku, Tokyo 169-8555, Japan

<sup>2</sup>Tanaka Kikinzoku Kogyo K.K., 2-73 Shinmachi, Hiratsuka, Kanagawa 254-0076, Japan

<sup>3</sup>Research Organization for Nano and Life Innovation, Waseda University, 513 Waseda Tsurumaki-cho, Shinjuku, Tokyo 162-0041, Japan

\*nomura@shoji.comm.waseda.ac.jp

Abstract - We propose a technique for the simultaneous fabrication of a through-glass interconnect via (TGV) and Au bumps using dry filling process of submicron Au particles. First, dry film resist holes were fabricated over glass through holes by photolithography. Next, submicron Au particles were filled into both the glass and resist holes, and sintered. We define a TGV sandwiched between two Au bumps as I- structure TGV. Crosssectional SEM images showed that the proposed I-structure TGV successfully fabricated without significant Furthermore, the glass substrate covered with thin Au film and the Au bumps were well sealed because the Au particles shrank during a sintering. Four-probe method using daisy chain revealed that the resistance of the single I-structure TGV was 0.11  $\Omega$ . These results indicate that the proposed fabrication method will be very useful for various applications of glass interposers or glass IC chips.

#### I. Introduction

Recently, miniaturization, energy savings and increased speed have been required in the field of packaging technology for various devices. Through silicon via (TSV) interconnect technology for the vertical integration of integrated circuits (IC) is one of the most promising technologies [1-3]. Although TSV technology can provide advantages such as a high wiring density, lower energy consumption and fast signal speed, it requires insulating layer formation when Si substrate is used as an interposer material in three-dimensional feedthrough interconnects. Moreover, conventional conductive material filling using electroplating requires long process time. Therefore, in this study we use glass substrate and dry filling process, proposing a technique for the simultaneous fabrication of through-glass interconnect via (TGV) and Au bumps [4]. The diameter of the Au bumps was larger than that of the TGVs so that the interspace between the glass substrate and the submicron Au particles could be sealed when the Au particles shrink during sintering.

#### II. METHODS

#### A. Fabrication Process

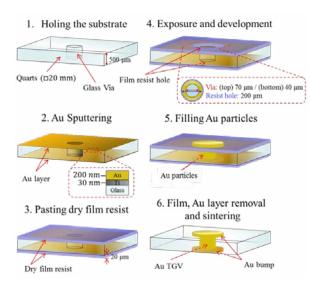

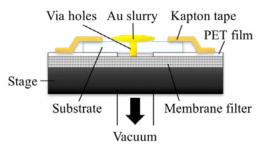

The fabrication process of the TGV and bumps structure named Istructure TGV is shown in Fig. 1. First, though holes were formed in a 500 µm-thick glass substrate using an electrochemical method. The diameters of holes in the top and bottom surfaces were about 70 and 40 μm, respectively (Fig. 1(1)). Ti/Au layers were deposited on the top and bottom surfaces of the glass substrate by sputtering to improve the adhesion between the submicron Au particles and the surface of the glass substrate (Fig. 1(2)). 38 µm-high dry film resists were laminated on the Ti/Au layers (Fig. 1(3)). The lamination was performed on a hotplate, and the temperature was under 100 °C. Resist hole patterns were concentrically formed on the glass through holes by photolithography. The resist hole was 200 µm in diameter and 38 µm in height (Fig. 1(4)). Submicron Au particles (AuRoFUSETM, Tanaka Kikinzoku Kogyo Co., Ltd.) were filled into the glass and resist holes by evacuating Au slurry coated on the top surface of the substrate from the bzack surface (Fig. 1(5)). Figure 2 shows a dedicated equipment for filling the Au particles. The substrate was heated at 110 °C on a hotplate for 10 min. The dry film resists were removed in acetone solution (Fig. 1(6)). The substrate was sintered at 200 °C for 10 min. The Ti/Au layers on the surface of the glass substrate was removed by Ar ion milling to isolate each bump electrically. The fabricated I-structure TGV was observed by scanning electron microscopy (SEM).

Fig. 1 Fabrication process of the proposed structure

Fig. 2 Equipment used for filling of submicron Au particles

# B. Electrical property

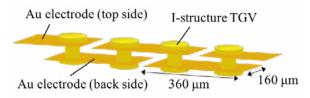

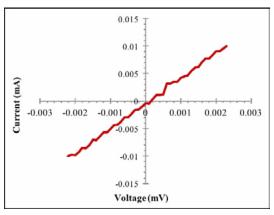

I-V characteristic of the I-structure TGV was measured by a four-probe method using a daisy-chain structure composed of 10 vias in series, as shown in Fig. 3. The Au electrodes were formed by pattering Ti/Au layer sputtered as adhesion layer (Fig. 2(2)). The width and length of the separate Au electrodes were 160 and 360  $\mu m$ , respectively. The I-V characteristics of the single Au electrode were also measured to determine the effect of interconnection resistance.

Fig. 3 Schematic image of the daisy chain

### **RESULTS & DISCUSSION**

#### A. Fabrication results

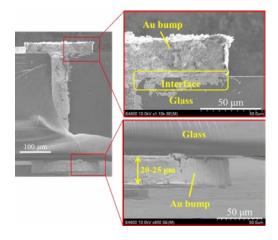

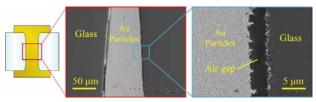

Cross-sectional scanning electron microscopy (SEM) images of the fabricated I-structure TGV are shown in Fig. 4. These images show that I-structure TGV was successfully fabricated without significant voids. The height of the Au bumps was about 25  $\mu m$ , although that of resist hole pattern had been 38  $\mu m$ . It is highly probable that the height decreased by the sintering and Ar ion milling.

Furthermore, the interface between the glass substrate and the Au bump was well sealed. This result indicates that the submicron Au particles shrank during the sintering and diffused to the deposited Au layer.

Cross-sectional SEM images of the TGV area are shown in Fig. 5. There is an air gap between the glass wall and filled Au particles due to the sintering process. However, it's expected that the hermeticity would be ensured because two Au bumps on the TGV work as the sealing cover. In fact, our previous results revealed that a leak late of a hermetic sealing device having the I-structure TGV satisfied a MIL-STD-883G standard [5].

Fig. 4 Cross-sectional SEM images of fabricated I-structure TGV and interface between the glass substrate and Au bump

Fig. 5 Cross-sectional SEM images of the TGV area

#### B. Electrical property

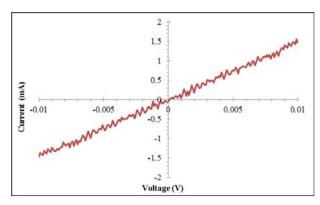

Figure 6 shows the I-V characteristics of the 10 I-structure TGVs connected in series, and Fig. 7 shows the Au electrode resistance. The calculated electric resistance of a single I-structure TGV was 0.11  $\Omega$ . This value is about 208 times larger than the theoretical bulk Au resistance of the same size. The theoretical resistance was calculated using expression (1), as follows

$$R = \rho L/A (1)$$

In (1), R is the resistance  $[\Omega]$ ,  $\rho$  is the electrical resistivity  $[\Omega m]$ , L is the length [m] of the wire and A is the cross-sectional area  $[m^2]$ . The measured value is likely to be affected by the I-structure TGV having high resistance. This is why the measured resistance was relatively high compared with the theoretical bulk Au resistance. Further studies are required in order to evaluate a uniformity of the degree of particle filling. This value, however, is sufficiently low for the practical use of the electrode. These results indicate that the proposed I-structure TGVs were electrically conductive and suitable for transmitting signals as an interconnection. Moreover, considering the sealing properties described above, the structure will be useful for various applications of glass interposers or glass IC chips.

Fig. 6 I-V characteristics of the fabricated I-structure TGVs (10 vias in series)

Fig. 7 I-V characteristics of the Au electrode

## III. CONCLUSION

In this study, we reported a novel technique for the simultaneous fabrication of a through-glass interconnect via (TGV) and Au bumps using dry filling process of submicron Au particles. The fabrication process of the structure defined as I-structure TGV involves following three main steps: (i) Deposition of an Au layer onto a glass substrate for improving the adhesion between the submicron Au particles and the glass substrate. (ii) Pattering of the dry film resist holes onto glass holes. (iii) Filling of submicron Au particles by evacuating Au slurry coated on the top surface of the substrate from the back surface. Cross-sectional SEM images showed that the Istructure TGV was successfully fabricated without significant voids. Furthermore, the interface between the glass substrate and the Au bump was well sealed. This result indicates that the I-structure TGV is expected to be applied to the sealing device. Moreover, The I-V characteristics measurement of the 10 I-structure TGVs connected in series reveals that the resistance of a single I-structure TGV was 0.11  $\Omega$ . This value is sufficiently low for the practical use of the electrode. These results indicate that the proposed fabrication method will be very useful for various applications of glass interposers or glass IC chips.

#### ACKNOWLEDGEMENT

This work is partly supported by Japan Ministry of Education, Culture, Sports Science & Technology (MEXT) Grant-in-Aid for Scientific Basic Research (A) No. 16H02349 and The authors thank for MEXT Nanotechnology Platform Support Project of Waseda University.

## REFERENCES

- [1]. J. Wolf, T. Dretschkow, B. Wunderle, N. Jurgensen, G. Engelmann, O. Ehrmann, "High aspect ratio TSV copper filling with different seed layers", *Proc. ECTC Conf.*, 2008, pp. 563–570.

- [2]. C. Song, Z. Wang, Q. Chen, J. Cai, L. Liu, "High aspect ratio copper through-silicon-vias for 3D integration", *Microelectron. Eng.*, 2008, pp. 1952–1956.

- [3]. J.-Y. Lee, S.-W. Lee, S.-K. Lee, J.-H. Park, "Through-glass copper via using the glass reflow and seedless electroplating processes for wafer- level RF MEMS packaging", *J. Micromech. Microeng.*, Vol. 23, No. 8, June 2013, 085012.

- [4]. H. Mimatsu, J. Mizuno, S. Shoji, T. Kasahara, K. Shih, K. Nomura, Y. Kanehira, T. Ogashiwa, "Simultaneous fabrication of a through-glass interconnect via and a bump using dry film resist and submicron gold particles", *IET Micro Nano Lett.*, Vol.9, pp. 532–5.

- [5]. K. Nomura, A. Okada, S. Shoji, T. Ogashiwa, J. Mizuno, "Application of I-structure though-glass interconnect filled with submicron gold particles to a hermetic sealing device", *J. Micromech. Microeng.* (in press).